华进半导体TSV喜获“第二十一届中国专利奖”银奖

随着摩尔定律放缓,一种不受其限制的高度集成封装方案应运而生——2.5D和3D堆叠技术。作为唯一可以满足如AI、数据中心等应用需求的封装方案,堆叠技术被应用于高、中、低端市场的各种硬件,包括3D堆叠存储、图形处理单元(GPU)、现场可编程门阵列(FPGA)和CMOS图像传感器(CIS)等。

硅通孔(Through Silicon Via,简称TSV)工艺是最早的堆叠技术。如今高端市场上,最热门的2.5D和3D集成技术就是3D堆叠存储TSV和异质堆叠TSV转接板。目前市场上已经出现的TSV堆叠方案包括CoWos、3D SoC、TSV interposer、3D Stacked Memory、Foveros以及Hybrid Bonding,方案供应商包括台积电、联华电子、英特尔、三星、海力士、美光、IMEC、格罗方德。TSV堆叠技术在5G通信、人工智能、消费电子、物联网、HPC和大型数据中心等高端市场,以及各类传感器等中低端市场得到广泛应用,前景广阔。据Yole预测,TSV在高端细分市场的收入将从14800万美元(2017年)上升至22.87亿美元(2023年),复合年增长率58%。

华进半导体自公司成立之初便集中精力开发TSV技术,并在国内率先实现了12吋硅通孔转接板的制造;基于此研发成果,华进还重点开发了Via-Las TSV、晶圆级封装等先进工艺,构建了较为完整的三维系统集成封装技术体系。目前,华进半导体有能力提供完整的从2.5D全套封装设计到硅转接板晶圆制造到2.5D组装成套一站式解决方案。目前,华进半导体已为国内外50余家知名企业提供了2.5D/3D集成封装技术服务。

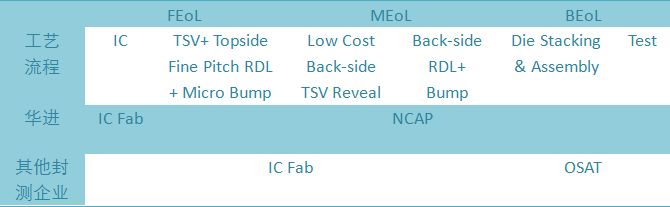

华进VS其他OSAT

科技创新与知识产权相互依存、相互促进。华进半导体在TSV相关的核心工艺均已布局专利。公司在TSV领域已申请320件专利,专利数量位居国内第三。值得一提的是,华进的“一种TSV露头工艺”专利在2019年斩获三项荣誉——第二十一届中国专利奖银奖、第十一届江苏省专利项目优秀奖、第十一届无锡市专利奖优秀奖。其中,中国专利奖,是专门对授予专利权的发明创造给予奖励的政府部门奖,得到世界知识产权组织(WIPO)的认可和支持,在国际上有一定影响。作为2019年度唯一入选中国专利奖银奖的封测企业,该荣誉对华进半导体是莫大的鼓励;同时,也是对企业知识产权实力的认可,对企业科技创新能力的肯定。

华进自主研发的TSV露头结构和工艺首次将干法/湿法相结合的Si刻蚀工艺应用在TSV背面露头技术中,让封测企业利用现有设备便可进行TSV硅转接板的制造,免去前道昂贵的CMP设备投入,无机介质工艺及有机介质工艺均可使用该专利技术。本技术成功打破了专利壁垒,突破了国外对2.5D集成的技术垄断。

一种TSV露头工艺

荣誉:

第二十一届中国专利奖银奖

第十一届江苏省专利项目优秀奖

第十一届无锡市专利奖优秀奖

专利简介:

硅穿孔(Through Silicon Via,简称TSV)工艺通过在晶圆中形成金属立柱,并配以金属凸点,实现晶圆之间或芯片与基板间的三维互连。由于芯片和晶圆的厚度小,要实现互连必须要对晶圆背面进行减薄工艺,露出TSV的导电铜柱。原始TSV露铜工艺是通过机械研磨将晶圆减薄至离TSV底部一定距离,然后通过湿法刻蚀或干法刻蚀将晶圆背面的硅去掉,露出TSV底部的铜。

此次,华进半导体参评专利所提出的TSV露头结构和工艺,是通过原创工艺方法实现的新结构,首次将干法/湿法相结合的Si刻蚀工艺应用在TSV背面露头技术中,使得封测企业采用现有设备可进行TSV硅转接板的制造,避免前道昂贵的CMP设备投入,无机介质工艺及有机介质工艺均可使用该专利技术。本技术成功打破了专利壁垒,突破了国外对2.5D集成的技术垄断。该专利可应用到各类集成电路封装领域的成套技术中,并且在5G通信、人工智能、消费电子、物联网、HPC和大型数据中心等高端市场,以及各类传感器等中低端市场得到广泛应用,前景广阔。目前,华进半导体基于该专利技术已为国内外50余家知名企业提供了2.5D/3D集成封装技术服务。

(华进半导体 封测联盟秘书处)