许居衍:中国工程院院士

黄安君:华虹半导体(无锡)副总裁 无锡市半导体行业协会秘书长

早前,我们从代表硅技术进步的各代DRAM产品生命周期中,分析计算了硅技术的S曲线,几种模拟方法得出S曲线的拐点发生在2014~2017(平均为2016) 年间[1]。届时,硅微电子产业及其R&D总投入均由增速转为减速,进入成熟发展期,摩尔定律(Moore's Law)开始失灵。早前的这个预测已为当今发展所印证。2016年3月,权威杂志《自然》发文指出,摩尔定律即将终结。与此同时,信守摩尔定律的英特尔公司在10nm节点上一再延后,并将其产品升级的“嘀嗒”(Tick-Tock)节奏模式,更改为“嘀(工艺)-嗒(架构)-嗒(优化)”。

现在不仅学术界,广大产业界和政界也都认为整个产业已经进入了“后摩尔定律时代”,纷纷部署“后摩尔”技术创新。例如:

2015年, 美国前总统奥巴马签署“国家战略计算推进计划” (NSCI)总统令,部署“后摩尔定律时代” 技术创新的支持。

2016年, “全球半导体技术路线图”(ITRS)史无前例地放弃了以摩尔定律为主导的思路,在IEEE重启计算创议下,更改为“自下而上”、应用推动技术发展的“全球器件与系统路线图”(IRDS)。

2016年,在中国半导体市场年会暨第五届集成电路产业创新大会上,工信部领导指出,“后摩尔时代”来临,多措并举加快集成电路转型。

2017年, 美国国防高级研究计划局(DARPA)启动了“后摩尔时代”的电子复兴计划。

2018年,欧盟提出有法、德、意、英等国29家公司参与的“后摩尔定律时代半导体增值策略”。

午后阳光依然灿烂,在追逐摩尔定律“狂欢”过后,人们将跳出定势思维,迎接新时代的新范式。

百花齐放,拓展创新视野

过去,在很长时间里,人们自觉地围绕摩尔定律的步伐,按部就班升级制程工艺、按部就班搭便车进行工程应用创新。但是,近年来,随着制程节点列车渐近“终点”,信奉摩尔定律的人们开始碰到进退维谷的困惑:跟随摩尔定律似乎能够支撑计算应用的进步,但它又时时阻碍着这种进步。

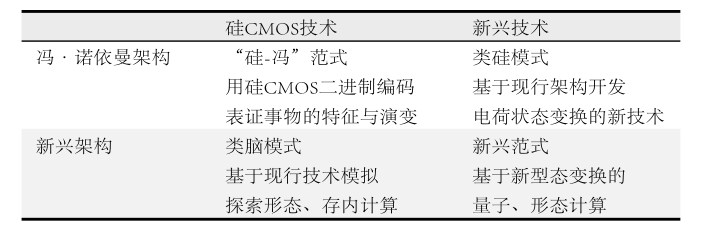

现在,这种“困惑”正在让业界人士看到,“放下摩尔定律这个定势思维,或许不是坏事”!为此,我们根据技术、架构对应用的关系,从技术与架构的分类法中看到(如表1),后摩尔时代的创新不仅“丰富多彩”,而且还隐含着某些哲理,这些,我们可以从以下各个子节介绍中看到。

表1

其中,硅CMOS技术与冯®诺依曼架构所形成的“硅-冯”范式,涉及技术和架构两方面的创新。前者包括MOSFET构建的CMOS(平面)和泛CMOS(立体栅FinFET、纳米线环栅NWFET 、碳纳米管CNTFET、Graphene FET等)技术,后者则是“在串行体制”内进行并行的体系结构创新。该范式尽管暴露了很多问题,但仍“欲罢不能”,还将在相当长的时期内主导着行业的发展。

类硅模式是在冯氏架构下的新兴技术创新,涉及NC FET(负电容)、TFET(隧穿)、相变FET、SET(单电子)等仍属电荷变换的非CMOS技术,由于能延续摩尔定律,受到了半导体业界的重视;

类脑模式是利用包括存储器在内的各种集成电路和3D封装模拟神经元特性,摸索存算一体等计算,因其并行性、低功耗的特点,已经在人工智能领域引起了广泛注意,并已获得某些工业应用;

新兴范式则涉及新的状态变换(信息强相关电子态/自旋取向)、新兴器件技术(自旋器件/量子)和新兴架构(量子计算/神经形态计算)。尽管商业化难度很大,但在基础探索的同时,也开始进入了产业视野。

架构创新,迎来黄金年代

丹纳德缩小(Dennard Scaling)、摩尔定律和计算架构是推动“硅-冯”范式技术进步的两股力量。在过去很长时间里,尽管架构也在不断创新,但硅CMOS技术每一年半到两年升级一大档,引诱了业界越来越倾向于“搭摩尔便车”以适时满足应用市场的要求,并因此造就了电子信息产业的“一代繁荣”。

但是,到2003年后,丹纳德(几何)缩小开始失效,随后的等效缩小主要依靠器件结构和新材料的创新,在维持硅芯片集成度和性能的增长趋势下,付出的代价是功耗不再满足丹纳德恒定电场的设想。

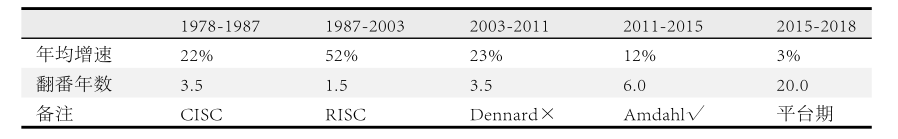

芯片功耗的上升制约了“硅-冯”范式特征产品-硅处理器的性能升级,从单核单线程硅处理器40年发展历程(见表2)可以看到,硅处理器的集成度和性能翻番规律,只在2003年前符合摩尔定律,之后由于丹纳德缩放失效、功耗密度不再不变,年均性能增长大幅下降,翻番年数由1.5年增加到3.5年,随后更一路下滑到几乎不再增长,进入了“平台期”。

表2

单程序硅处理器进入平台期的时间是2015年,而正是这一年ITRS升级到ITRS2.0,并于2016年更改为IRDS。这些情况表明,丹纳德缩放和摩尔定律的终结,使得“硅-冯”范式的创新主体由技术转向架构,从而迎来架构创新的黄金年代[2]。

近几年来,为应对大数据、人工智能等高算力的应用要求,主流芯片架构发生了重大变化,以期增加每瓦、每个时钟周期内可处理的数据量,为数十年来芯片架构转变奠定了基础,使得异构计算(HC)、领域专用计算、可重构计算等得到了很大发展。架构创新所涉及的要点有以下几个方面:

最大限度地减少数据移动,同时又使数据流最大化;移近计算与存储、有效利用、提高内存带宽;提高软件对硬件的适配性、提高软件重用性和抽象水平;消除不必要的精确性;容忍适当的近似计算;优化成本、性能、能耗。

异构集成,重塑产业生态

1965年,摩尔以“在集成电路中塞进(Cramming)更多元件”为题发表被誉为“定律”的预测;之后,行业依此思想由小规模集成到大规模集成,一直发展到今天“塞进”了数以百亿元件的片上系统(SoCs),把半导体工业推到一个“无以复加”的高度。

但“全则必缺,极则必反”(吕氏春秋·博志)。在工艺制程精细到十几个、几个纳米的今天,在同一个工艺节点上,把诸多元件“填鸭式(Cramming)”地做成系统,不仅不能同时优化SoCs上不同元部件的特性,还会因此造成“浪费”。另外还因为构成复杂,需要不同团队的无缝协同,拉长了设计时间,极大地提高了产品成本。例如14nm制程工艺,仅仅验证花费就高达5千万美元)。

随着节点缩小,工艺变得越来越复杂且昂贵,在经典平面缩放耗尽了现有技术资源、应用又要求集成更加灵活和多样化的今天,若在芯片中还想“塞进更多元件”,就必须扩展到立体三维,从异构集成(HI)中找出路。

2015年(又是这一年)Marvell公司在旧金山的ISSCC(IC奥林匹克赛会)和上海的IC China上提出了模块化芯片(Modular Chip,MOChiTM )概念:采用DRAM存储器,CPU、GPU计算元件,LTE Modem、WiFi、南桥等“模块化”裸芯片,通过异构封装堆叠成智能手机和笔记本电脑处理器,而这些模块以前就是一颗SoCs芯片。其中特别要指出的是,异构集成所堆叠的、可置于计算近处的高带宽存储器(HBM),在SoCs中是难以实现的。

2017年美国国防高级研究计划局(DARPA)在其启动的电子复兴计划中提出名为CHIPS(Common Heterogeneous Integration and IP Reuse Strategies)的项目,参加单位有英特尔、美光、新思科技以及波音、洛克希德等公司。计划的目标客户是商业和军事应用;计划的思路是建立一个由多方提供的、称为Chiplet的模块化裸芯。Chiplet是一种裸管芯(die)形态的IP,译为“芯粒”比较恰当[3]。它以“搭积木”的方法,采用先进封装堆叠连接成“多芯粒模组”(MCM)。这是对SoCs的替代,从过去基于IP设计,变为基于芯粒(Chiplet as a IP)设计,它将促进从架构探索到模组实现的EDA工具发展;同时它也是对过去“多芯片模组”(MCM)的螺旋复归,从过去芯片(Chip)的组装到现在基于芯粒(Chiplet)的异构集成。这些情况表明,技术对应用的需求,都要回归到“使用最经济资源,实现最理想功能 ”的电子系统基本要求上来。

基于异构集成的芯粒具有很多优点,例如:可用不同节点制造,因而不仅优化了各自的性能,而且还因结构紧凑可兼善良率与成本;可以灵活且方便组装系统,因而能捕捉市场窗口,缩短上市时间;可方便修改设计,更换异构计算中的定制加速部件/协处理器,从而鼓励、推动芯片架构创新。

在这些优点刺激下,芯粒模式发展迅速。2018年10月,为制定芯粒开放标准、促进芯粒生态系统、催生低成本SoCs替代方案的ODSA (Open Domain-Specific Architecture)组织成立,发起单位仅7家,但半年后就增加到53家,去年底则已扩大到70多家,反应热烈。值得指出的是,这次芯粒所诱发的产业变革跟上一次Fabless+Foundry完全不同,它是由Intel(IDM)、AMD(Fabless)、TSMC(Foundry)这样的大企业主导的,因而来势汹涌,从提出芯粒重用策略到今天才短短几年就已经形成热潮。

芯粒是半导体产业方向的重大转变,它必将重塑行业生态。芯粒虽然对拥有先进封装能力的IDM、Foundry有利,但产权有可能来自系统商、IP商和Fabless等各个行业部门,而且封测商也占据了与以前稍有不同的重要地位。由芯粒模式所重塑的行业生态将影响着半导体以外的整个电子信息行业。

推陈出新,科学实践突破

“硅-冯”范式是一个极为庞大而复杂的体系,在70多年赶班车式的发展历程中,既积累了天文数字的宝贵资源,又暴露了难以解决的问题,从而导致人们既想沿着这条路走下去,以收获成果,但在途中又碰到阻碍这种成果实现的壁垒。为解决这个矛盾,业界出现了跟半导体更新换代类似的科学实践。

半导体产业是一个集极端精密(线宽达纳米级)和极大规模(仅纳米级方孔就数以亿计)于一体的工程科学,产品制程工序数以百计,因此在技术与产品更新换代过程中,釆用了“嘀”(工艺升级)-“嗒”(产品换代)策略,即在工艺升级时产品(比如存储器)架构保持不变,便于找出工艺问题,而在工艺稳定后再换代产品,集中解决新产品本身的问题。

在多元相关复杂的“硅-冯”范式中,早在多年前就已经开始了“嘀”-“嗒”的进步策略,表一中的类硅模式是一个例子,即在冯氏架构不变情况下,沿着电荷状态变换,寻找可代替CMOS的器件技术,其中除了改善MOS晶体管亚阈值的负电容FET、二维材料FET等外,还进行了诸如纳电子机械NEM relay之类的全新机制的技术探索。另一个例子是表一中的类脑模式,它利用现行器件技术模拟非冯架构,其中特别是改变存储与计算分离的“存内算计算”和区别于“程序流”的“脉冲或尖峰传递信息的事件驱动”计算。

缩小变数、聚焦问题的“嘀”-“嗒”研究策略,既能为颠覆性的创新打基础,又满足了市场对高算力应用的要求。

超越摩尔,回归物理基础

从物理角度看,冯氏计算的性能与频率正相关,而硅CMOS技术的功耗却正比于频率的3次方,“硅-冯”范式碰到了难以逾越的功耗墙瓶颈。一位被誉为可重构计算之父的德国教援R. Hartenstein在2016年提到:“70年前采用冯®诺依曼原理是历史上最大的错误之一 ”,某种程度上表明现在已经到了探索新的替代范式的时候了。

道生万物,万物复归于道。技术与计算早期都是始于“模拟”,后来才慢慢“数字化”。经历了计算与网络的第一次数字化浪潮、移动计算的第二次数字化浪潮和现在正进入的以数字智能为特征的第三次数字浪潮,计算技术今后不知道还会不会进一步发展。但基于人类认识的螺旋上升特点,在“非0即1”精确可控的高度“数字化”后,又会“复归”于“模拟”。

自然界有两个神秘而奇特的现象,一个是诡异的量子叠加与纠缠现象,一个是至今难以说清的脑意识现象,这些现象中的状态变换,不是“非此即彼”,而是具有概率结构或事件驱动性质的模拟计算。

在摩尔定律逐渐示微的过程中,波粒二象性的量子计算和基于新功能材料的脑灵感神经形态计算必将加速发展,人类有可能在半导体晶体管和存储程序计算发明百年后,迎来新兴的器件技术与计算架构的工程化。届时,我们又将看到从现在的工程应用创新回归到物理基础创新。颠覆性基础创新将把人类推向更高的文明。

原文刊载至《电子科学技术》

参考文献

[1] 许居衍,“硅微电子发展前景预测”,中国电子学会第五次学术年会大会特邀报告,1992

[2] David Patterson “A New Golden Age for Computer Architecture: History, Challenges, and Opportunities”,https://www.acm.org/hennessy-patterson-turing-lecture

[3]许居衍“复归于道:封装改道芯片业” ,中国半导体封装测试技术与市场年会,2019.9.9

(来源:无锡市半导体行业协会)